研究紹介

IoE 社会のエネルギーシステム~革新的デバイスの適用によるエネルギー供給コストの定量的評価~

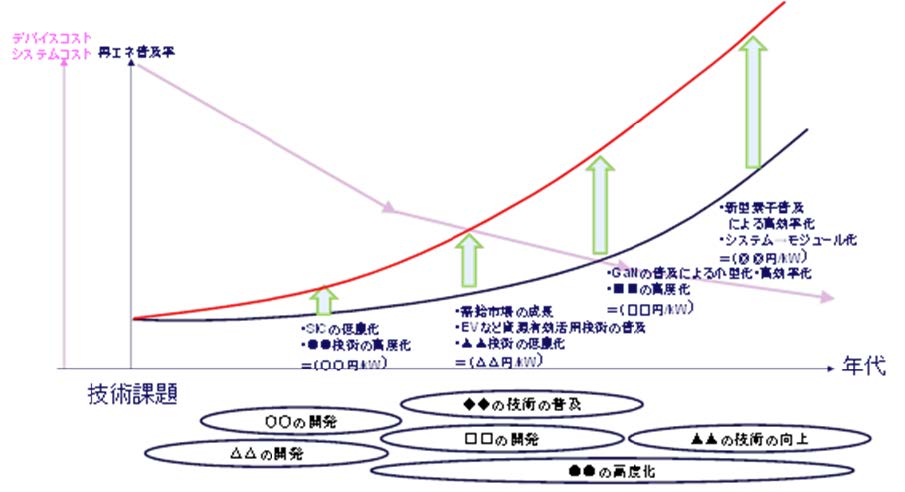

PE 技術貢献ロードマップのイメージ

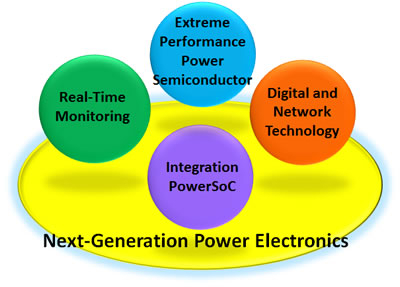

Society5.0 の具現化に向けては,さらなる温室効果ガスの削減とエネルギーの多様化を両立させることが課題の一つである。この課題を解決する鍵の技パワーエレクトロニクス技術(以下,PE 技術とする)がある。PE 技術は,エアコンやパソコンの電源装置などにおいて省エネや小型化などへの寄与が大きく,応用先は多岐に亘っている。近年の太陽光発電などの再生可能エネルギーを電力系統へ連系させる際の回路にも用いられている。このPE技術においては,炭化ケイ素(SiC)や窒化ガリウムに加え,近年では酸化ガリウム(Ga2O3)など革新的な半導体素子の開発が進んできており,これらの適用により,機器の小型化・高効率化など機器側の利点のみならず,電力損失の低減やエネルギーの利用率向上など,エネルギー供給システム全体においても利点があり,PE 技術の普及を推進していく必要がある。

一方,PE 技術の普及を推進するには,新たな技術が導入された場合の社会的な効果を予め定量的に示して,社会コスト低減効果を共有する必要がある。加えて,普及の障壁となる技術的課題を整理して,技術者を含め多くの人と認識を共有する必要がある。

本研究では,エネルギーマネジメントシステムを構成するエネルギー供給路全体に革新的なPE 技術を適用することで得られる技術的な便益(電力損失の削減,電力品質の向上など)や経済的な便益(社会コスト削減効果など)を定量的に明らかにする。これにより,社会実装に向けた指針が明確になり,さらなる技術進展の速度を向上させることに寄与する。

本研究テーマは内閣府・戦略的イノベーション創造プログラム(SIP)のテーマの一つとして採択されている。

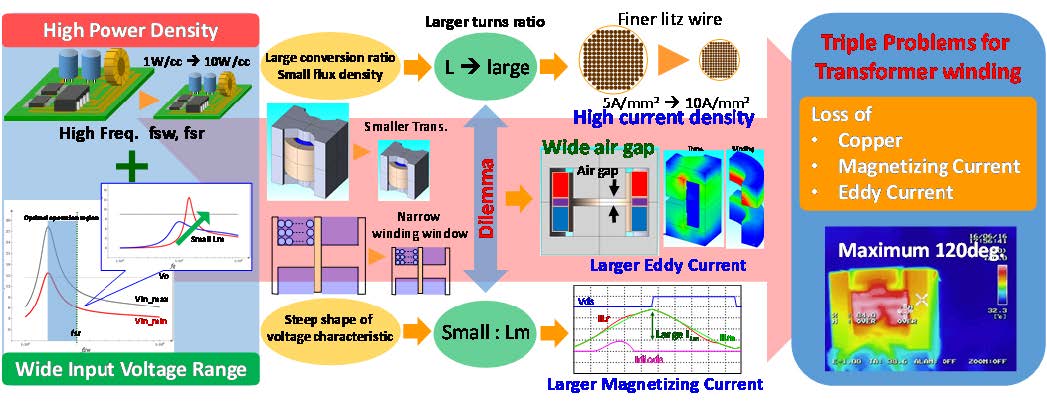

広範囲な入力電圧変動に対応した電流共振コンバータの高電力密度化に関する研究

広入力電圧範囲・高電力密度化におけるトランス設計の課題

LLC コンバータに代表される電流共振コンバータは補助回路なしでソフトスイッチングが実現でき小型・高効率・低ノイズの特徴を有することから民生・産業機器用電源として広く利用されている。また、LLCコンバータの同期整流技術の導入によりさらなる高効率化が実現できるようになったことからこれまで利用されてこなかったアプリケーションへの適用が期待されるようになってきた。

一方、システム構成の面からこれまでの適応状況を見てみると、LLC コンバータはPFC コンバータと組み合わせて利用する場合が殆どである。そのため、LLC コンバータは入力電圧変動が小さい場合を想定して設計される。最近では、バッテリーを入力とするシステムへの利用が期待されており、広い入力電圧範囲への適応と高電力密度を同時に満たすことが要求されている。しかし、上記要求を同時に満足しようとすると下記3 つの理由によりトランス巻き線の損失が著しく増加することがこれまでの研究で明らかになっている。

1. 巻き線の細径化による銅損の増加

2. 小励磁インダクタンスによるコア損失の増加

3. トランスコア間の広空隙による渦電流損失の増加

これらの問題はLLC コンバータの広入力電圧範囲化及び高電力密度化の実現を著しく阻害する。上記問題の発生メカニズム及びその解決手法についてはこれまでに報告しているが、軽負荷時の制御性が著しく損なわれるという新たな問題が発生している。

本研究では、新たに発生した問題を解決するための設計手法や制御手法について検討している。

超小型電源が切り開く次世代電力ネットワークシステムの研究開発

低炭素社会実現のための前提となる高度電力化社会では、多くのパワーエレクトロニクス機器が部品化され大量に使用されることを考えると、それら機器の高効率・小型化(高電力密度化)が必要になる。現に、パワーエレクトロニクス機器は15 年で1桁の高電力密度化が進んでおり、グリーンエレクトロニクス分野の中でも集積化パワーエレクトロニクスシステムの研究開発は益々重要となってくる。また、ビッグデータ、クラウドコンピューティングの到来と共に情報通信機器の電力消費量は爆発的に増大し通信用パワーエレクトロニクス技術の高度化による高効率化と小型化が必須となってきている。電力ネットワークシステムでは様々なセンサが大量に用いられ、これらへの電力供給が大きな課題となることが予想され電源の高度集積化技術の重要性が高まっている。

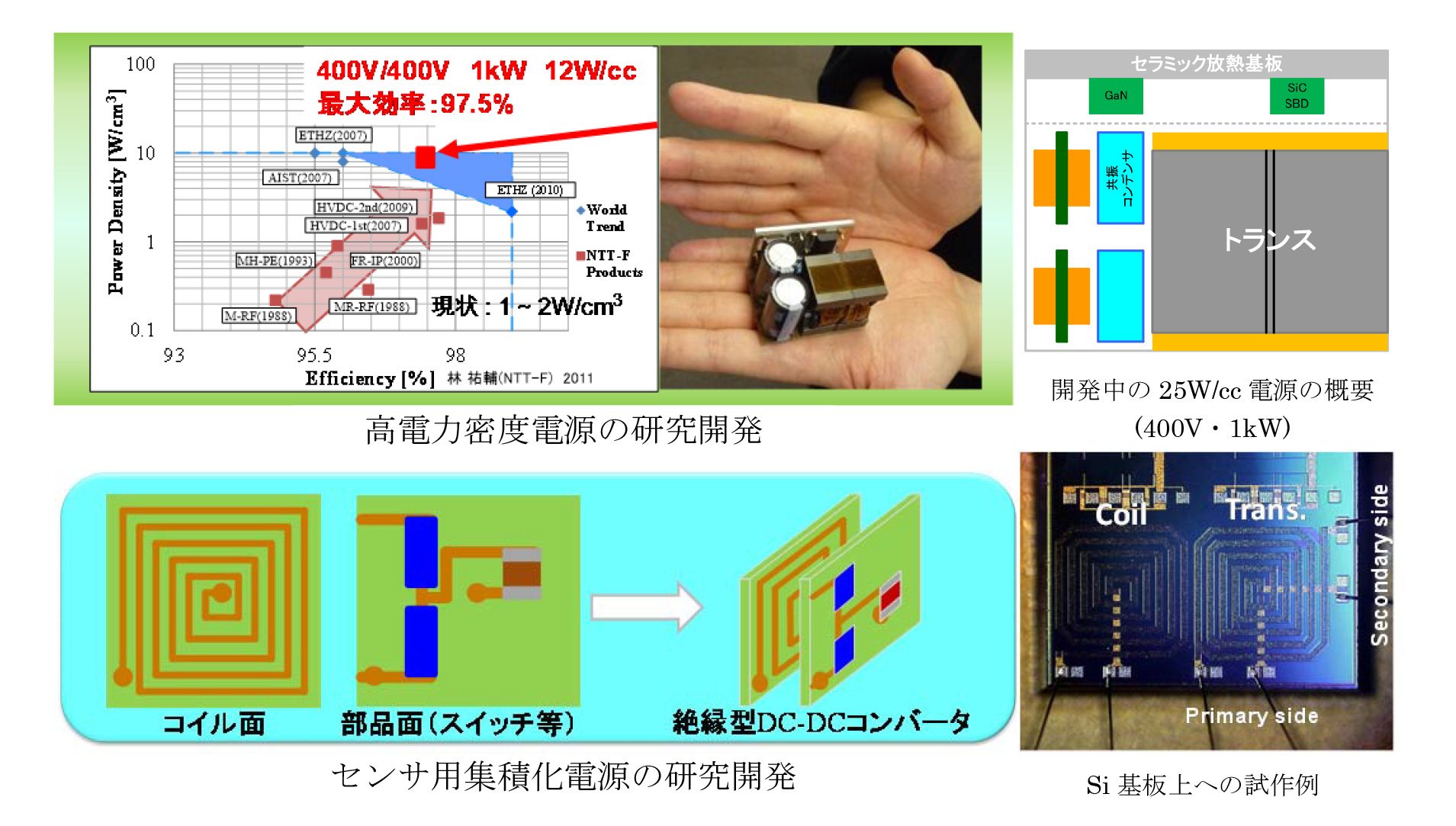

本研究では、データセンターにおける次世代電力ネットワークシステムに対応する超小型電力変換器の研究開発を行っており、現状、400V・1kW 出力で効率97.5%・電力密度12W/cc を達成している(一部アジア成長研究所での成果を含む)。さらに、回路方式及び冷却部分の改良やSiC やGaNにより25W/cc を超える高密度電源の開発を進めている。また、センサ用集積化電源(パワーSoC 電源)の開発も進めている。

電源の究極の小型化を目指したPower-Supply on Chip 研究

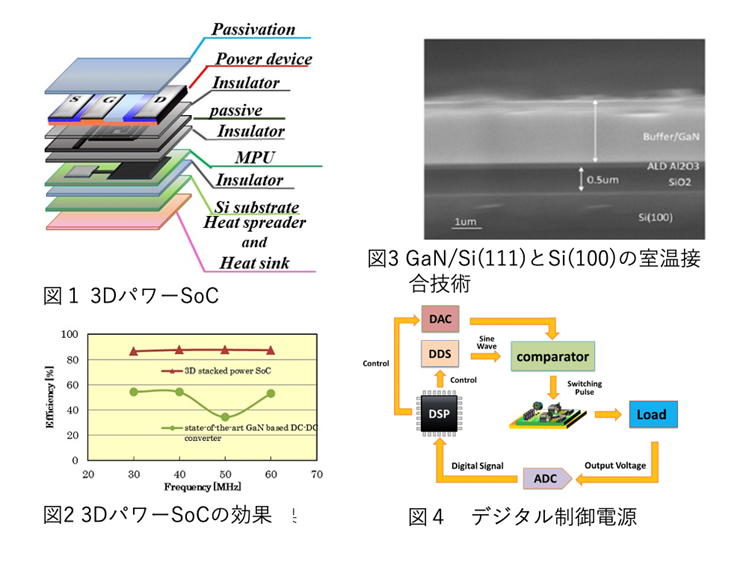

電源の研究トレンドは小型化であり、電源の究極の小型が実現できるPower Supply on Chip (Power SoC) が注目を集めている。我々の研究グループでは、Siパワーデバイスに比べて高周波(数十MHz〜数百MHz)・高降圧比(高い入力電圧、低出力電圧)で高効率動作が期待できるGaNパワーデバイスの使用が可能な3次元Power SoCを提案した(図1)。3次元Power SoCは、各種デバイスを3次元に積層して実装するため寄生インピーダンスを極限まで減らすことができ、30MHzで損失を約1/3低減できる(図2)。

3次元Power SoCではGaNパワーデバイスとSi-LSIをデバイスプロセス終了後積層するため、室温でのウエハー接合技術の開発が必要となる。我々の研究グループでは、GaNパワーデバイスとSi-LSI をface to face で接合することを想定し、Si(100)基板とGaN/Si(111)基板を室温で接着し、Si(111)基板を除去する技術を開発した(図3)。

3次元Power SoC はLSIやMicro Electro Mechanical Systems (MEMS)プロセスで製造するため大量生産が可能で低コスト化が可能な反面、大量生産に見合う用途開発が必要となる。このため、様々な用途に対応できるデジタル制御への期待が大きい。従来のデジタル制御電源ではスイッチング周波数の1000倍程度のクロックで動作するDSPが必要であるが、クロック周波数200 MHzのDSPとDirect Digital Synthesizer (DDS)を用いて5 MHzで動作するデジタル制御電源を実現した。

3次元Power SoCを設計する際、様々な物理現象を考慮する必要がある。これらを考慮した設計が可能な”Virtual prototyping 技術”を提案した。

パワーエレクトロニクス回路用キャパシタ評価

キャパシタ評価研究の概要

インバータ等のパワーエレクトロニクス回路で使用される直流リンクキャパシタはパワー半導体デバイスや磁気素子に比べ寿命が短く,高パワー密度化の制約だけでなく機器の信頼性低下を招いている。故障を完全に防ぐことは困難であるが,健康状態のモニタリングにより故障時期を推定できるようになれば信頼性が向上する。

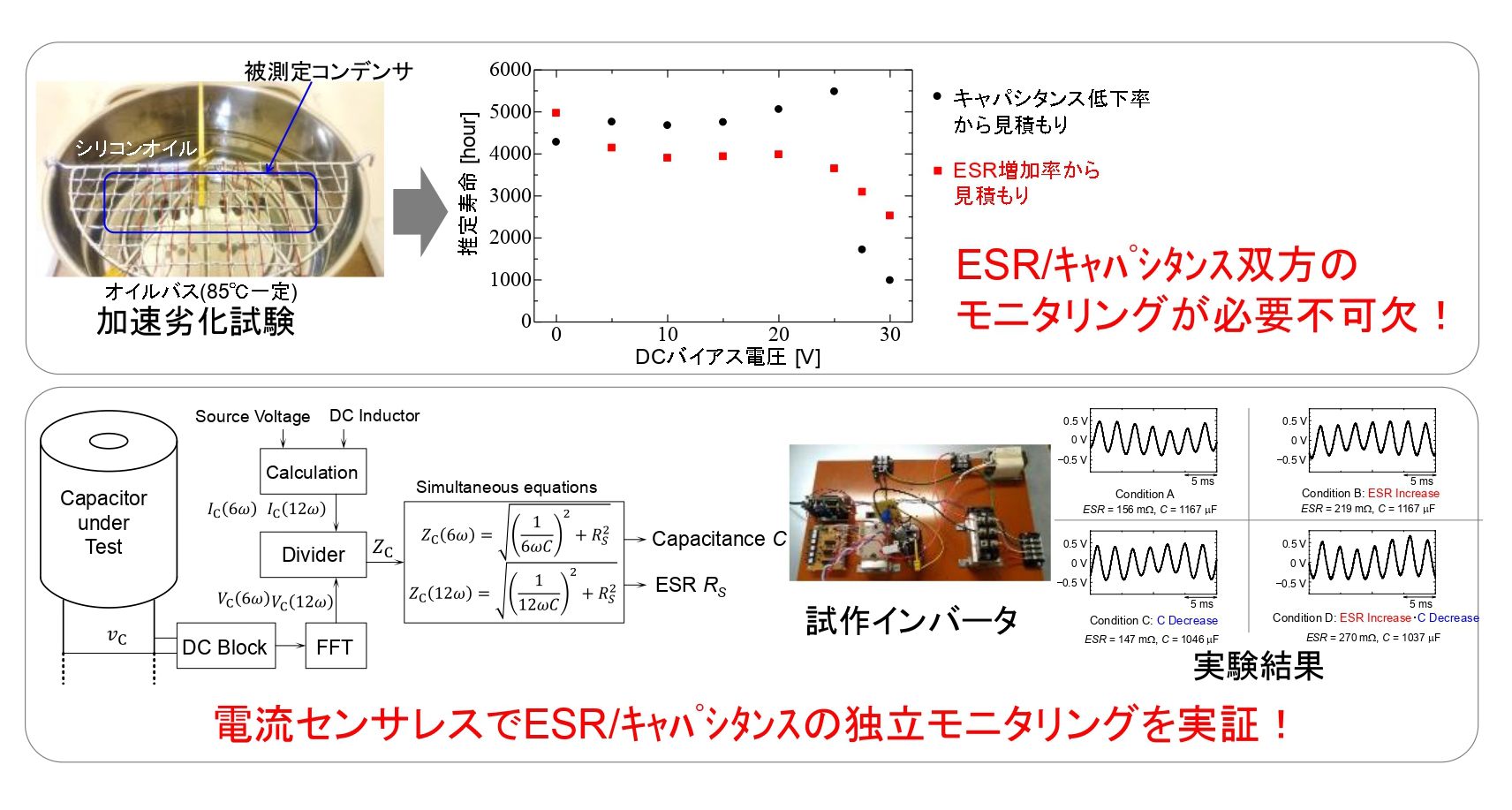

本研究ではこれまでに,加速劣化試験によりキャパシタ劣化の直流バイアス依存性を実験的に解明し,キャパシタの健康状態のモニタリングには従来使用されていた等価直列抵抗(ESR)だけでなく,キャパシタンスの観測も必要不可欠であることを明らかにした。その知見をもとに,ESR/キャパシタンス双方をオンラインでモニタリングする手法を開発している。

実電圧・実リプル電流波形からキャパシタ寿命の指標であるESR とキャパシタンスを独立に抽出するためには2方程式必要であるが,従来用いられていた実効値を用いる手法では1方程式しか得られない。そこで,実電圧・実リプル電流に高速フーリエ変換(FFT)を適用し周波数成分毎に分解し複数の方程式を立式することでESR/キャパシタンス双方を抽出するモニタリング手法を提案した。この手法は,コンデンサを取り外すことなく,かつ検出用の電流なども必要としないため,コンデンサの実動作環境におけるオンラインのモニタリングが可能である。したがって,インフラ設備用など運転停止ができないインバータにも応用可能である。回生の必要ないモータ駆動において広く利用されているダイオード整流器・三相PWM インバータを用いたシステムに提案法を適用し,ESR/キャパシタンスの独立なモニタリングを実証している。

モニタリング手法の実現にあたっては低コスト化のためセンサ部品の削減が求めらる。そこで,インバータの回路動作の解析によりキャパシタ電流を理論的に算出できることを解明し,電流センサレスで低コストのモニタリング手法を実証している。

次世代高分子固体コンデンサのパワエレシステム評価

次世代高分子コンデンサのパワエレシステム評価 概要

パワーエレクトロニクス機器は小型化・低コスト化のためさらなる高パワー密度化が要求されており,機器の中で大きな体積を占めるコンデンサの小型化対応が急務になっている。これに加え, SiC やGaN などのパワー半導体は低損失であるだけでなく,200℃程度の高温動作が可能である。コンデンサはパワー半導体の直近に配置する必要があり,コンデンサも高温環境に曝される。以上からパワエレ機器の高パワー密度化に向けて今後必要となるコンデンサは次の条件を満たす必要がある。1)アルミ電解コンデンサの高容量密度と,フィルムコンデンサの高リプル電流密度の特長を兼ね備える。2)従来の電解コンデンサの耐熱温度125℃を超える175~200℃の耐熱性を持つ。この要件を満たすコンデンサとして導電性高分子固体コンデンサが注目されている。現状は低い電圧で絶縁破壊が生じるため,製品レベルでは160 V 以下の耐圧に限られているが,誘電体の欠陥・界面制御と新規導電性高分子開発によりパワエレ機器で要求される高耐圧化が期待されている。

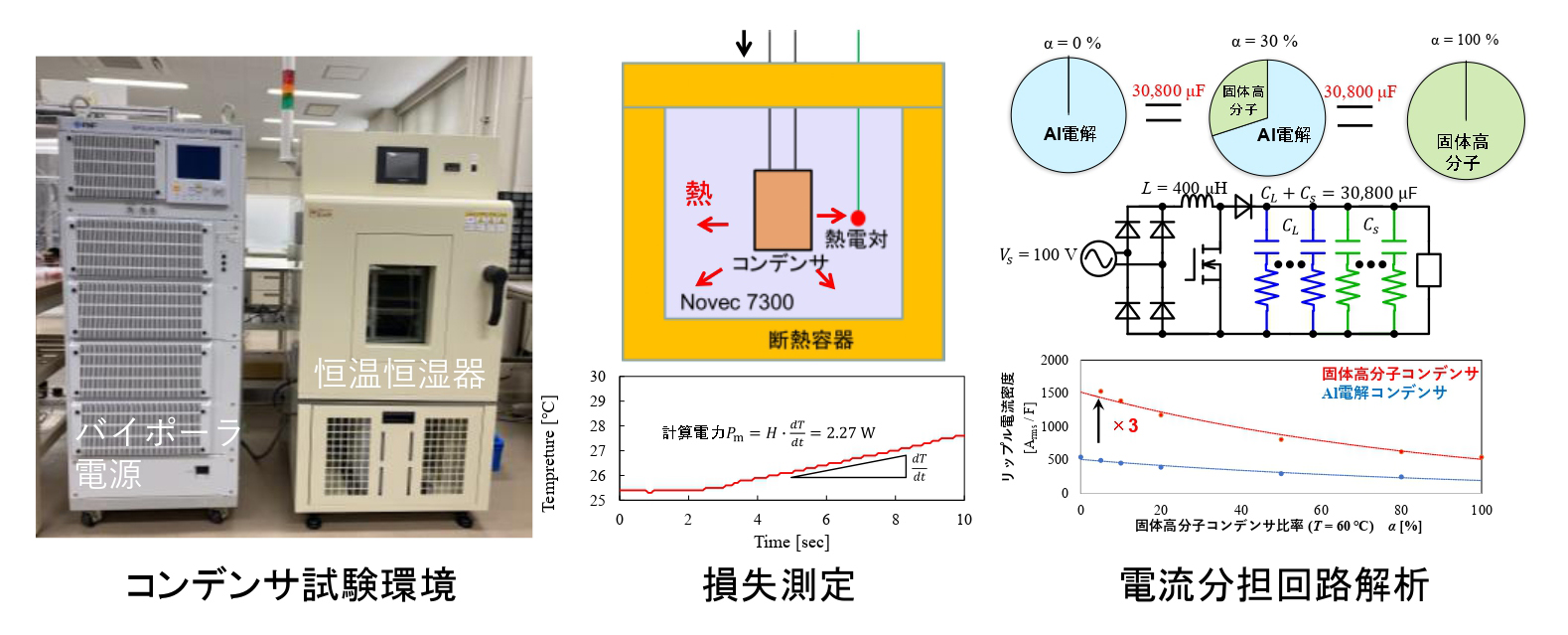

本研究では上記の次世代導電性高分子固体コンデンサのパワエレシステム評価として下記の項目を行っている。

1)カロリー法を用いた損失測定

パワエレ機器の高周波化だけでなく固体コンデンサ自身の低損失化が進むと,電気的にコンデンサ損失を測定することが困難になる。カロリー法を用いることで電圧・電流波形に依存せずに損失を測定する環境を構築している。

2)コンデンサ並列接続時の電流分担解析

単相PFC 整流器など幅広い周波数帯を有するリプル電流条件下では,高容量密度の非固体コンデンサと,高リプル電流密度の固体コンデンサを並列接続して使用することが想定される。この場合の最適な分担比について研究している。

3)モニタリング手法の開発恒温

恒湿器を用いた劣化試験環境を構築し,パワエレ機器の実動作条件における劣化傾向を分析し,その知見をもとにモニタリング手法の具体化を目指している。

本研究は,文部科学省「革新的パワーエレクトロニクス創出基盤技術研究開発事業」の採択プログラムのひとつである。

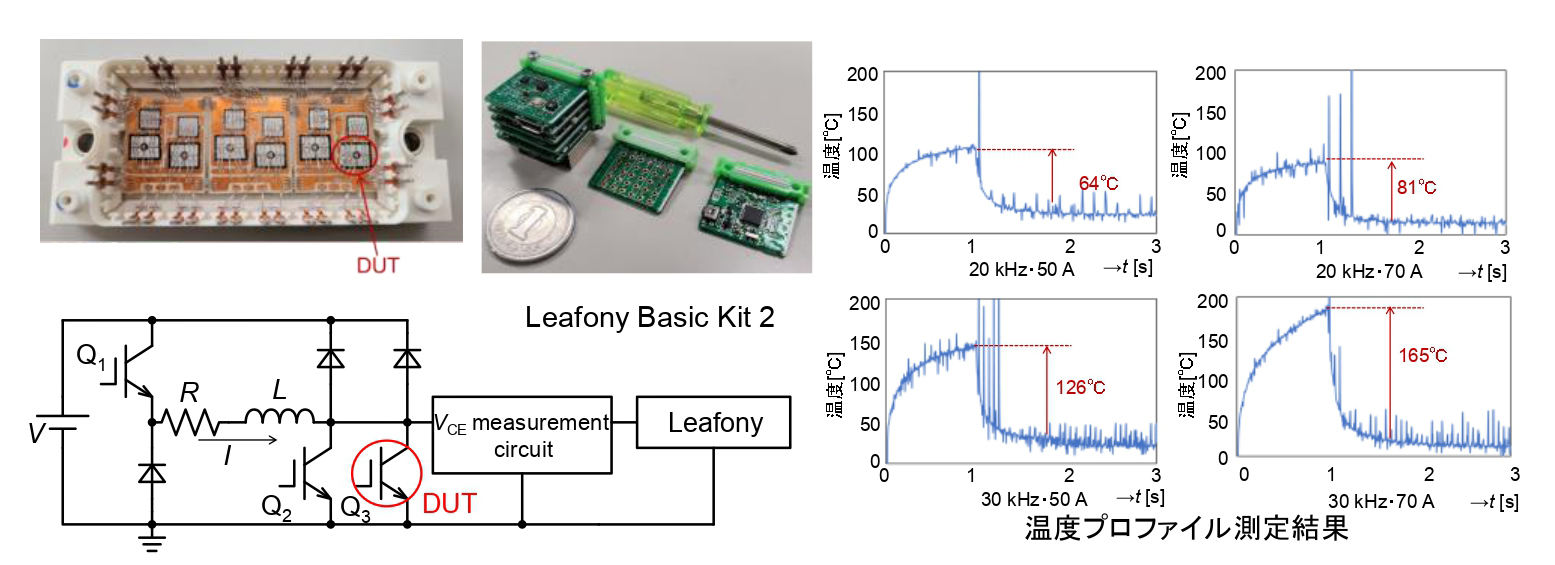

インバータ連続運転条件におけるIGBT モニタリング技術

IGBTモニタリング技術の概要

従来,パワーモジュールは一定のパワーサイクルストレスを繰り返し加えてその前後で劣化度合いを評価するパワーサイクル耐量試験を実施してきた。今後のネットワークに接続されたパワエレ機器では運転時のストレスによる劣化を観測する状態を観測し,故障や劣化度合いを検出する必要がある。

本研究では,インバータの連続運転状態において常にストレスが変動する条件における熱抵抗の計測技術を開発している。運転状態における電流・電圧・温度を算出からモジュールで発生する損失を算出し,熱抵抗の初期値からモジュール内のチップ温度を演算する。演算した温度と計測した温度の違いから熱抵抗の増加を検出する。

パワーモジュールの劣化・故障を検出する上では温度依存性を持つオン電圧のVCE(sat)のモニタリングが有効である。VCE(sat)のリアルタイム測定にあたっては,IGBTのオン時・オフ時のコレクターエミッタ電圧の差が大きく,ノイズ耐性の観点から測定が困難である。そこで,VCE(sat)検出回路を設計・製作し,IGBTオフ時の高電圧を阻止しつつ,数ボルトオーダのオン電圧VCE(sat)のみを測定可能としている。これに加え,低コスト・超小型IoTプラットフォームであるLeafony Basickit 2 を用いてノイズ耐性の高いディジタル測定環境を構築している。測定したデータの送信にはUSBアイソレータまたはBluetooth を使用することで,グランド電位を分離した状態で測定できるため,コモンモードノイズの低減に寄与する。

基礎検討として,IGBTモジュールの熱応答を確認するためチョッパ回路として連続動作を行った際の温度プロファイル測定を行っている。1700V75A6in1モジュールを用いて,温度プロファイルの負荷電流およびスイッチング周波数に対する依存性を確認している。これによりモジュール内蔵のサーミスタを使用する手法に比べ高精度に温度測定可能であることを確認している。また,パワーサイクル試験により熱抵抗が10%増加したパワーモジュールの連続動作時の温度プロファイルを実測と予測で比較し,定格電流に近い大電流動作時では予測との差異から劣化検出が可能であるという結果が得られている。

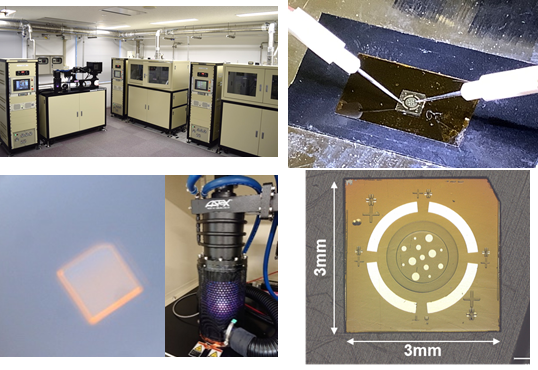

高耐圧ダイヤモンドパワーデバイス構造設計

(左上)次々世代パワー半導体試作装置(学研都市共同研究開発センター205室)

(左下)ドーピング薄膜合成中の様子(右上)デバイス特性計測 (右下)ダイヤモンドpinダイオード

パワーエレクトロニクス機器を構成するパワーデバイスの高性能化が、低炭素・省エネルギー社会の実現に不可欠であり、シリコンデバイスの性能限界を超えるパフォーマンスを実現する次世代パワーデバイスとしてSiCやGaNなどのワイドギャップ半導体が市場に投入されつつある。ワイドギャップ半導体の一つで高い臨界電界が特徴であるダイヤモンドは、高電圧を扱う直流送電などのパワーエレクトロニクスで新しい半導体材料として期待されている。

当センターではp型、n型、ノンドープダイヤモンド薄膜の合成可能な次々世代パワー半導体試作装置を導入し、超高耐圧ダイヤモンドパワーデバイスの開発、パワーデバイスの集積化を目指した表面実装技術の開発を行っている。これまでに、ダイヤモンドpinダイオードを試作し耐圧層 1.5μmで200V以上の耐圧を確認し、同等の性能をもつ1/20サイズのデバイスを開発した。デバイス試作および独自設計のダイヤモンドTEGを用いた高耐圧化のための要素技術開発およびスイッチングデバイスの開発を行う。

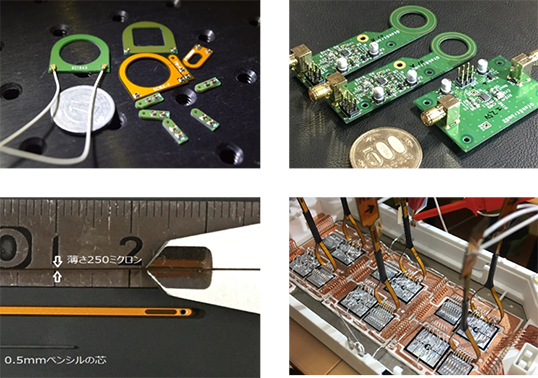

超小型電流センサ開発

独自開発:超小型ロゴスキコイル電流センサ

プリント基板上への集積化と信号処理IC技術と融合した、新しい概念の電流センサを開発した。特殊なプリントパターンと独自の信号処理技術で1000分の1に小型化・低コスト化を実現。1A以下~1000A以上までの広い電流範囲とDCから100MHzまで周波数レンジをカバー可能。

電気自動車や太陽光発電などに使われるパワー半導体や、サーバー用スイッチング電源のプリント基板上に集積化するなど様々なパワーエレクトロニクス機器への応用が広がる。専用ソフトウエアの開発で、電流検出だけではなく故障診断などの機能を付加できることも特長である。既存センサに比べ体積を1/1000に低減、低コスト化を実現。磁気飽和が起こらないため、小型ながら数1000A以上まで計測可能である。計測器用アクセサリ、インバータ出力電流検出や二次電池電荷モニタ用など様々な応用が見込まれる。

さらに厚さ0.25㎜、幅1.8㎜の超薄型センサも開発した。本センサ―により、並行平板配線のすき間や、部品間の隙間、ボンディングワイヤの下部など、今までセンサを挿入できなかった箇所の電流計測が可能になる。

今後、更なる小型化と高精度化、低ノイズ化に向けて開発を進める。

本研究の一部は、研究成果展開事業 大学発新産業創出プログラム/大学・エコシステム推進型スタートアップ・エコシステム形成支援(2022年度採択)の支援を受けたものである。

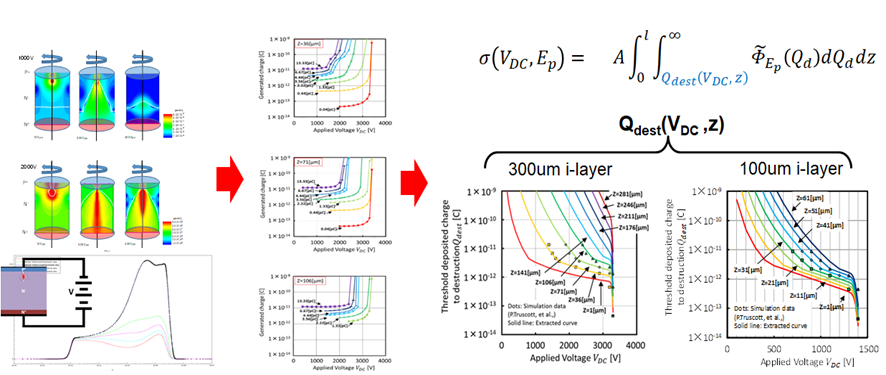

高電圧デバイスの宇宙線故障率

電動航空機や宇宙ステーション用パワー半導体の故障率計算方法とTCAD解析の例

一般的に地上で用いられるパワー半導体でのSEB故障率はZeller氏による式など、経験式アプローチが広く用いられている。この方法は設計値の入力のみで簡易的に故障率を計算できることが特徴で、何か月にも及ぶ加速試験と比較して多くの利点がある。しかし、経験式アプローチは地上で用いられるパワー半導体の故障率の計算にしか適用できないという問題があり、航空機の飛行高度や宇宙で利用されるパワー半導体デバイスには適用できない。

そこで、本研究ではあらゆる高度に対応した簡易で効率的な故障率算出のための数式アプローチを提案する。これは、あらゆる高度条件での宇宙線フラックススペクトルに対応した統一的な故障計算手法である。本提案手法の特徴は、宇宙線粒子の故障断面積と宇宙線フラックススペクトルを数式上で分離したことであり、その結果、地上、航空高度、宇宙環境など、あらゆる放射線環境下での故障率計算を可能にしている。本論文では、数式導出までの原理と導出過程及び、2種類のPiNダイオード(i層長:100μm及び300μm)に対する、地上から高度60kmまでのSEB故障率を具体的に計算している。本研究の成果により、航空宇宙用の高耐圧パワー半導体の宇宙線による故障を最小限に抑える設計が可能となり、航空宇宙分野でのパワー半導体デバイスならびにそれらを用いた機器の高信頼化に貢献できる。

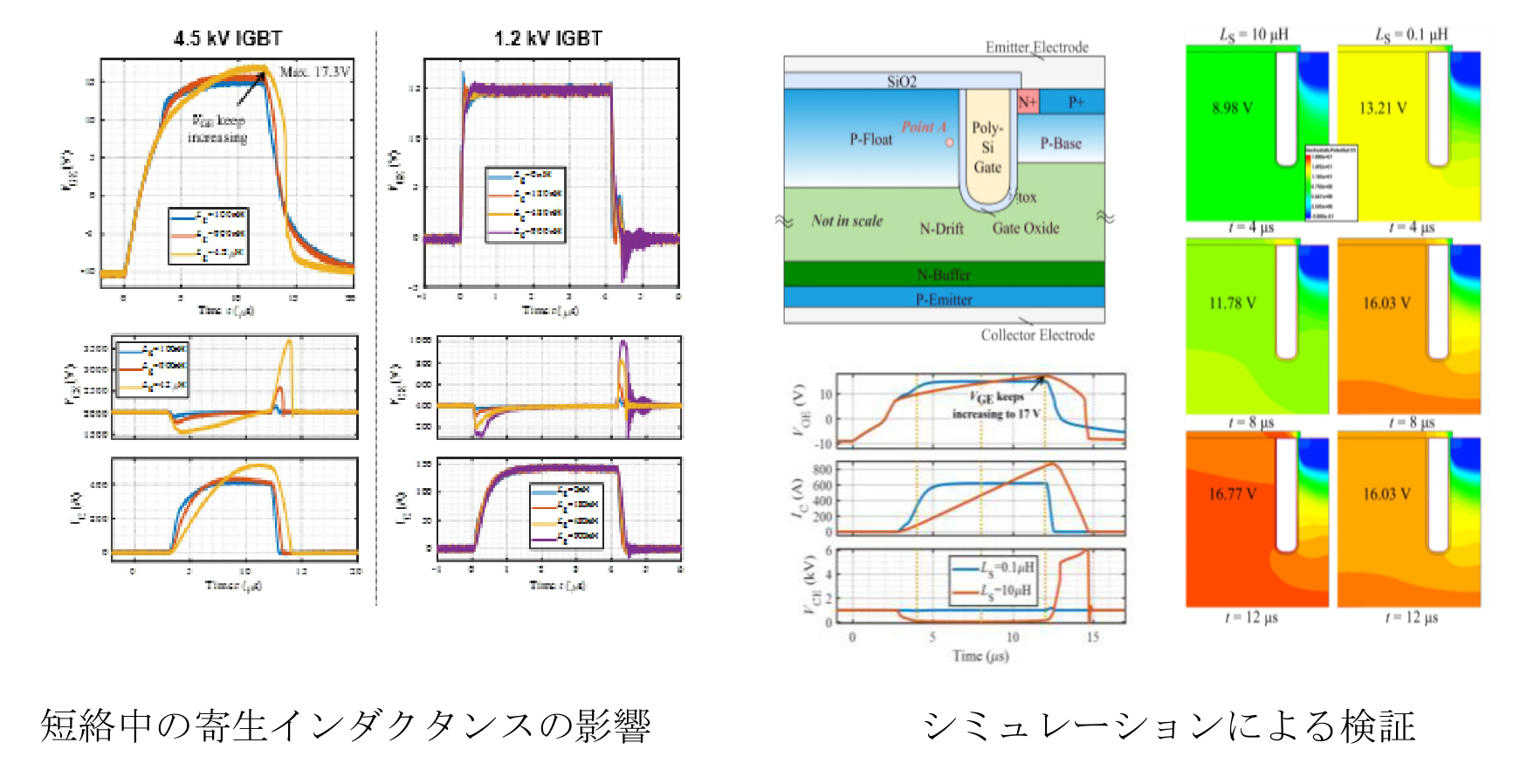

高電圧IGBTの短絡動作に対する寄生インダクタンスの影響

高耐圧IGBTの短絡時に発生するゲート電圧の変調について原因の分析を行った。高耐圧IGBTは数千アンペアクラスの製品があり、短絡時の挙動の解明が重要である。特に短絡時に発生するゲート電圧のオーバーシュートは、短絡電流を増加させるだけでなく、短絡保護時のスパイク電圧を増加させるなどの影響が考えられる。

本研究では寄生インダクタンスの影響を考慮した条件で、大容量IGBTの短絡時のゲート電圧オーバーシュートの解析をTCAD及び実験により行った。

その結果、寄生インダクタンスが大きい条件ではゲート電圧が本来の値を超えて増加を続け、結果として過大なコレクタ電流が流れ、短絡保護を困難にしていることが分かった。

この現象はPフロート層を持つIGBTで顕著にみられ、ゲート配線の最適化に加え、デバイス構造の見直しも有効だと思われる。

本論文はAPEC2023 The Applied Power Electronics Conference )にて公表済みである。

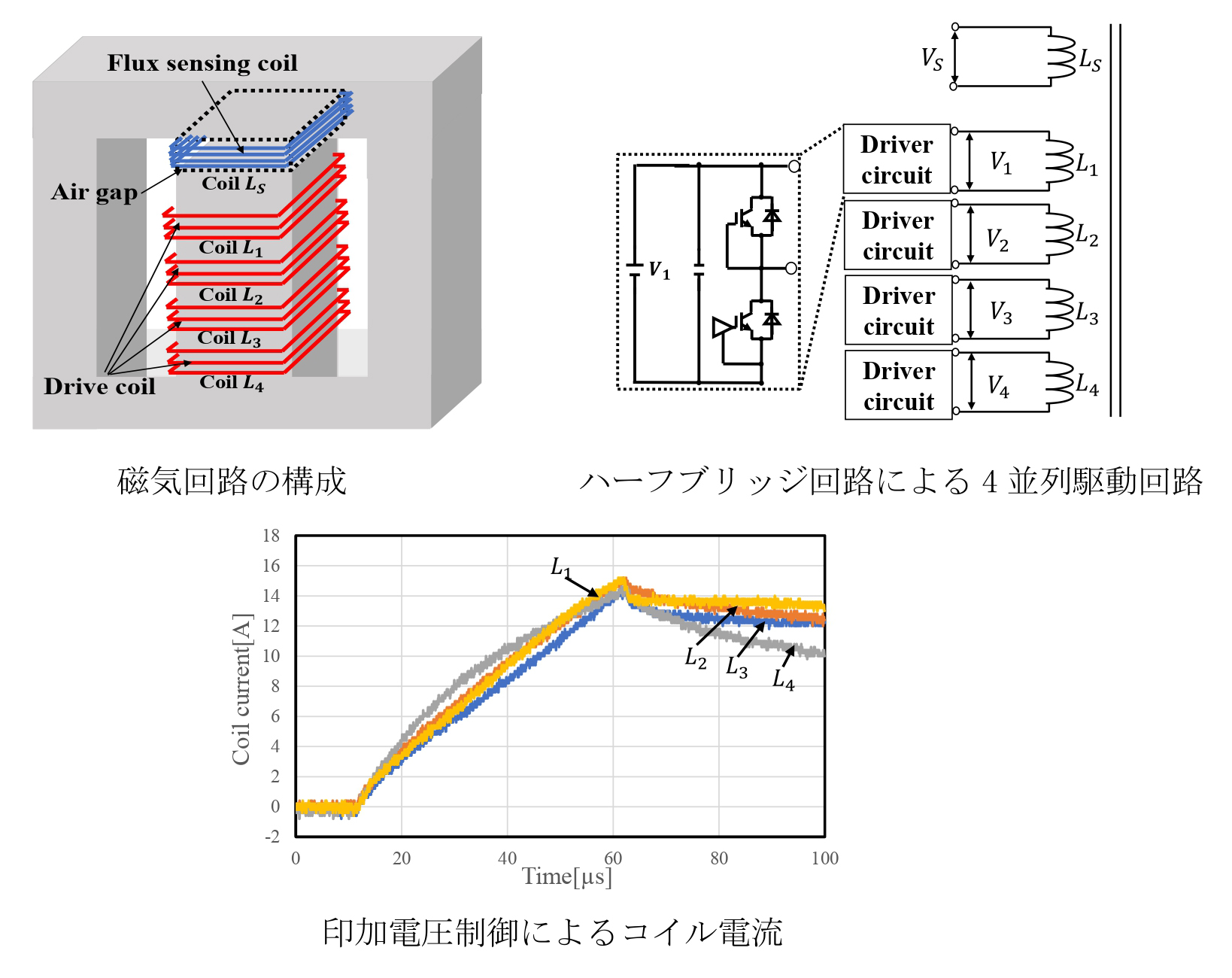

複数巻線を用いたMRM用高磁束発生回路

低回転域での効率改善のために、MRM(Magnet Reversal Motor)が提案されている。MRMは、ステータの永久磁石に対して強い磁界をパルスで与え、永久磁石の磁極をロータの回転に応じて入れ替えることでトルクを発生するモータである。MRMの駆動には、100~200μ秒のパルスで1テスラ程度の高磁束密度が必要であり、駆動回路には大きな電流および高い電圧の両立が必要になる。今後MRM 実用化され大容量化が進むと駆動回路の構成が困難になると予想される。

本研究では、複数のコイルをステータコアに配置し個別の単相インバータで駆動することで電圧や電流を低減する手法を提案した。各インバータを同期させ、複数のコイルを駆動すると、コイル配置の非対称性からコイルに流れる電流が大きく不均一になる。ステータ・ロータ間のギャップに近いコイルには電流が集中しやすいことが考えられ、電流不均一は特定のインバータに負担が集中し、故障など不具合の原因となる。本研究では、MRMのステータコアに配置した複数のコイルを個別の単相インバータで駆動する際に、各コイルに流れる電流を均一にする手法を実験により実証した。

本研究は、JST 未来社会創造事業JPMPMI20E1 の支援を受けたものである。

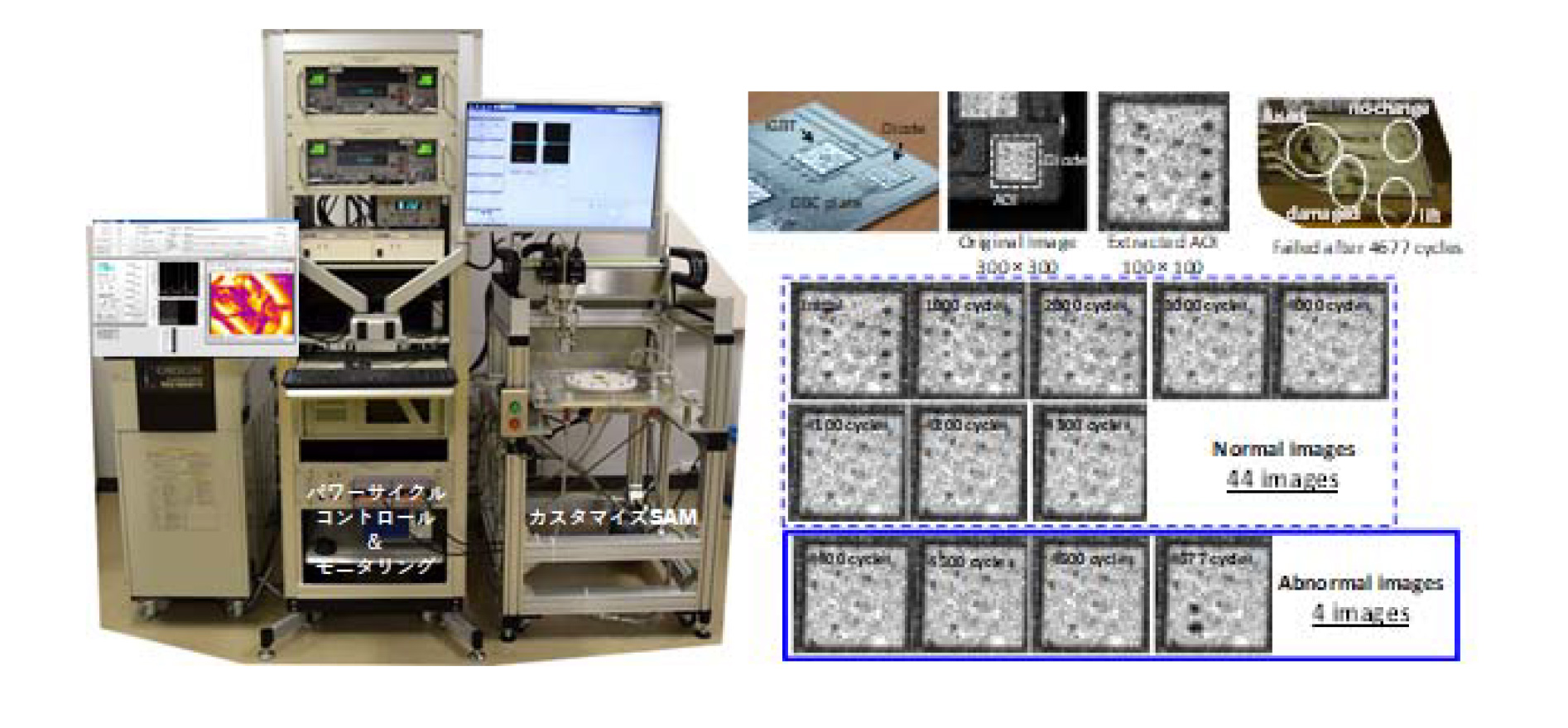

パワー半導体の高信頼化を促進するリアルタイムモニタリング技術

複合型パワー半導体検査装置

パワー半導体の故障原因の特定では、

①過去の故障データに基づく統計的手法

②高ストレスによる加速試験と故障の再現

③FA(Failure Analysis)等による原因分析

を駆使して行われてきた。しかし、近年パッケージ構造等の複雑化が進み上記の方法だけでは原因の特定が困難になってきている。

開発したリアルタイムモニタリング装置は、故障のトリガとなる現象を時間経過とともにミクロなレベルで記録・観測するツールで、デバイスの内部の構造変化をストレス条件である電流・温度分布などをリアルタイムで取得し、故障の瞬間に何が起こっているかを明らかにする。本システムは、様々な劣化現象やそれらが引き起こす故障の様子を捉えることで、局所的なストレスと故障の原因となるミクロな現象の関連付けを可能にし劣化のモデル化にも力を発揮する。

プロトタイプで得た知見から新規開発した現システムは、ユーザビリティの向上によりサンプルをセットすれば簡単な設定のみで測定が開始でき、パワーデバイスの故障解析から材料の劣化試験など幅広く対応できる。現在は、画像処理やAI による特徴抽出・故障判断技術の研究を進めている。

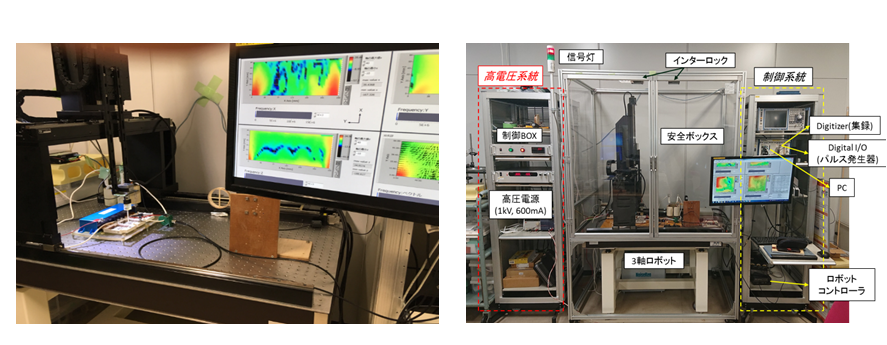

パワーエレクトロニクス機器用ノイズ計測評価

独自開発のノイズ計測システム

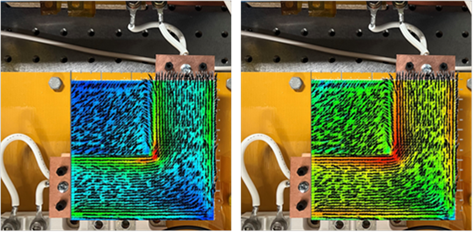

L字銅板電流集中測定結果

パワーエレクトロニクス(パワエレ)機器は、省エネルギー性や制御性に優れている反面、スイッチング動作時の急峻な電圧、電流の変化により、高周波の電磁波ノイズを発生する。発生した電磁波ノイズは、周辺の電子機器に悪影響を及ぼす可能性があるため、パワエレ機器の開発にはノイズ対策が必須となる。しかし、従来のノイズ評価は開発の最終段階で行われるため、開発期間の長期化、高コスト化が問題となっている。そのため、開発の初期段階でノイズ評価を行い、ノイズ源を特定できるシステムが求められる。

本研究では、開発の初期段階で可能なダブルパルス試験によるノイズ計測手法を提案した。通常のノイズ強度に加えて磁界ベクトルを可視化することで、より高精度なノイズ源特定を可能にする。

開発した計測システムにより、最小限の電源設備、冷却器、制御回路でのノイズ評価が可能となり、ノイズ設計のフロントローディングに貢献する。本計測システムを用いて磁界測定を基に擬似的な電流のカラーマッピングとベクトル表示を可能にした。電流表示を可能にすることで、これまでのシステムでは見えなかった電流集中している箇所を可視化した。

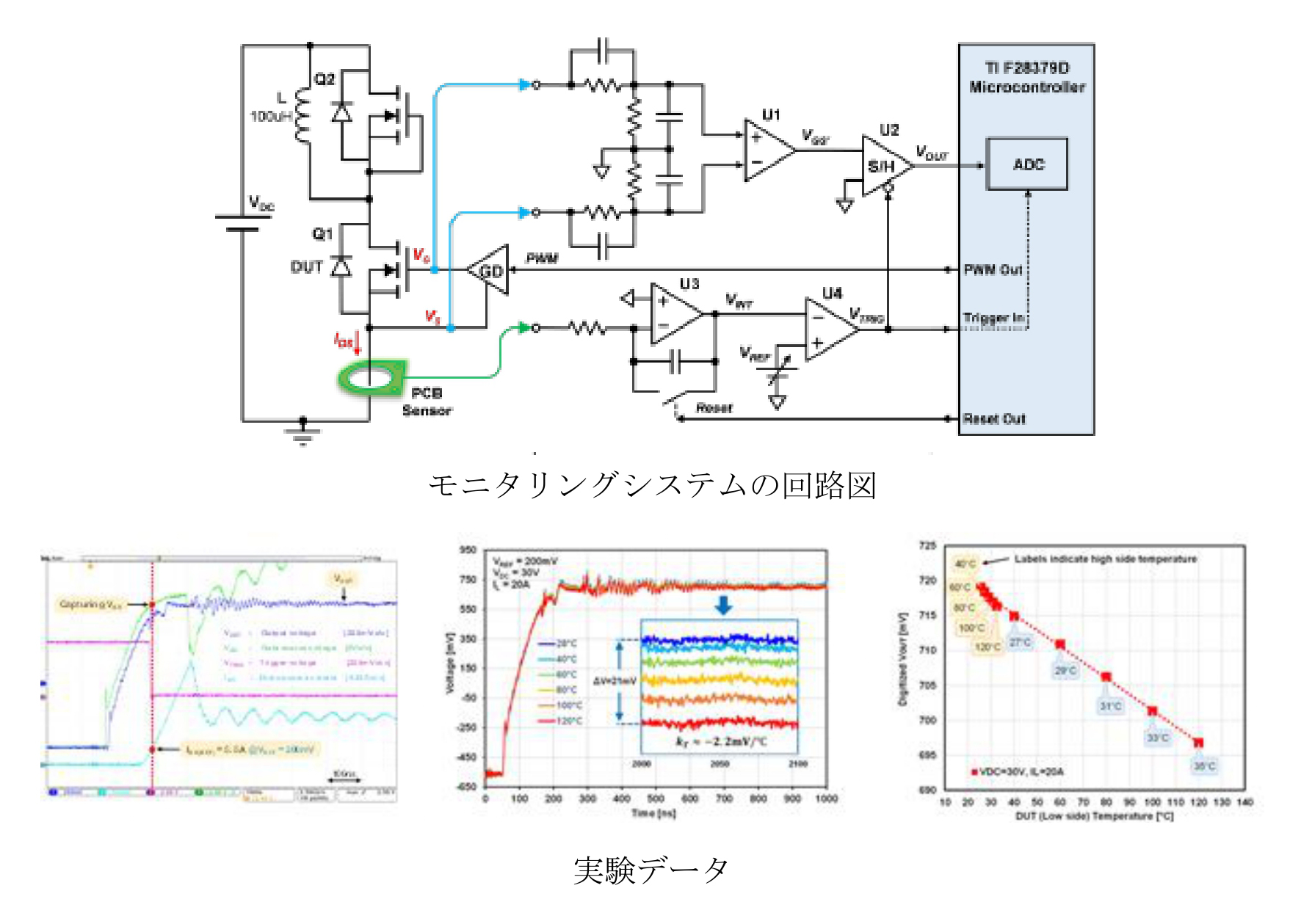

パワー半導体の接合部温度推定のためのモニタリングシステム

高信頼性への要求が高まる中、動作中のパワーデバイスのコンディションモニタリングは重要性を増している。パワー半導体デバイスのジャンクション温度は、モニタリングの重要な指標である。そこで、温度センシティブ電子的パラメータ(TSEP)の一つであるゲートしきい値電圧の変化をモニタリングしてパワーMOSFETのジャンクション温度を推定する新しい方法を開発した。

パワーMOSFETのジャンクション温度を抽出するため低コストPCBロゴスキコイルを用いる方法を提案した。この方法により、ゲートソース間電圧を所望の電流レベルで取得可能とりパワーMOSFETのモニタリング機能を高度化することが可能となる。システムを実現するために、マイクロコントローラー上の16ビットADCによってモニタリング出力電圧をディジタル化している。本システムは、他の測定器などを必要としないスタンドアロンで動作し、-2.2mV/℃でジャンクション温度の変化を電圧としてモニタし続けることが出来る。

本研究成果はISPSD2023 (International Symposium on Power Semiconductor Devices andICs)で公表済みである。

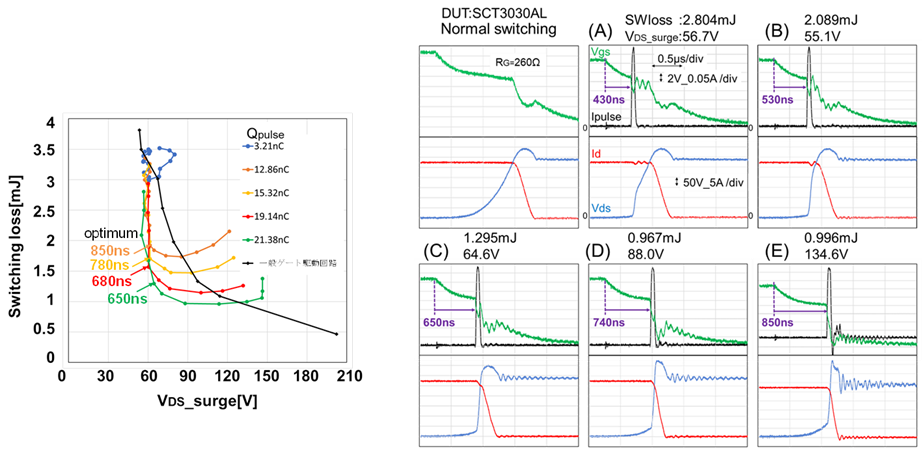

デジタルゲートドライブによるIGBTのトレードオフ改善率評価

(左)各電荷量におけるトレードオフカーブ比較

(右)通常スイッチング波形と電荷パルス制御回路入力時のスイッチング波形

パワー半導体のサージ電圧とスイッチング損失はトレードオフの関係にあり、双方の低減が困難であった。この問題を解決するためにデジタルゲートドライブ(DGD)方式が研究されている。しかしながらDGD方式には、ゲートドライブ回路が複雑であり最適駆動波形の探索に時間がかかるという課題があった。そこで本研究では最適化探索を必要とせず簡易な回路を付加するだけで、DGD方式と同等の効果が期待できる方式を新たに提案し、その有効性について実験により実証した。その結果電荷パルス制御回路を用いてミラー期間の電荷を放電させることでパワー半導体の損失を改善した。サージ電圧を軸として同軸比較したとき、57.0%の改善率を実証した。またターンオフの立下り時にミラー期間までの電荷を放電することで56.2%の改善率を実証した。一回のスイッチングを行いダイナミック入力特性の取得をすると、放電電荷量を算出することができ、損失改善することができる電荷パルス制御回路を作製した。実際に電荷パルス制御回路でミラー期間までの電荷を放電させた際損失の改善を実証した。

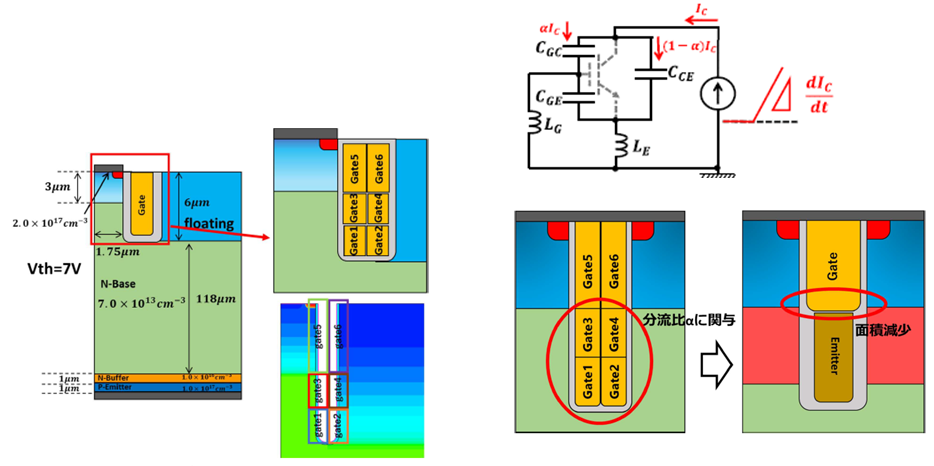

TCADシミュレーションによる理論検討

ゲート電流懐石におけるゲート分割構造 スプリットゲート構造採用による電流変化

MOS ゲート駆動デバイスを用いたスイッチング電源やモータドライブなどの高速スイッチング回路では、高速スイッチングによって高dV/dt が発生する。高dV/dt によってデバイスが意図せずターンオンする現象をセルフターンオンと呼び、損失増大や故障の原因となる。この現象はdV/dt 破壊とも呼ばれ、高速スイッチングによって発生した高dV/dt に基づいて解析されてきた。しかし、更なるスイッチング速度向上とともに浮遊インダクタンスの影響が大きくなっており、従来のdV/dt に基づいた解析では対応できなくなっている。

本研究ではコレクタ電流dIC/dt に着目し,dIC/dt とゲート浮遊インダクタンスがセルフターンオンに直接影響することを示した。ゲート浮遊インダクタンスLG、dIC/dt、エミッタ浮遊インダクタンスLE に基づくセルフターンオン発生の基準を明確にし、基準を基に新たな対策を提案した。

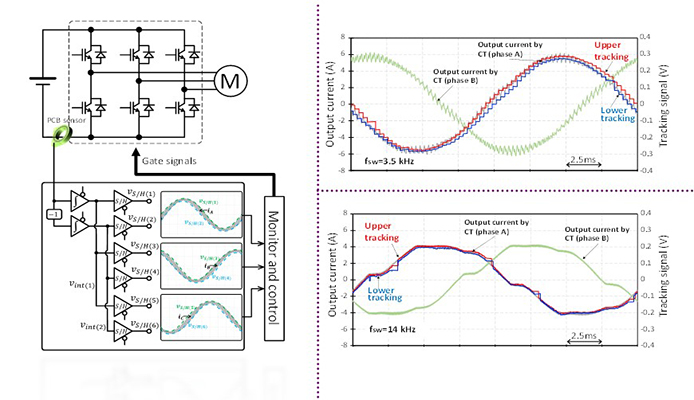

パワーモジュール内の電流計測技術

電圧源インバータの開ループ出力(制御あり)

インバータシステムには通常、磁性体コアを用いた電流センサが使用されており、システム全体のサイズとコストに大きな影響を及ぼしている。新たに開発したプリント基板(PCB)ロゴスキーコイルセンサは,構造が簡単で,コストが低く,高周波領域での感度が良いため,スイッチング素子を用いたインバータやコンバータシステムで使用するのに最適なセンサである。これまでの研究により,2つ以上のPCBセンサに基づく電流再生方式が明らかにされている。

本研究では,1個のPCBセンサを用いたインバータシステムのための実用的な電流フィードバック制御を提案する。インテリジェントパワーモジュール(IPM)に組み込まれた相補的なアナログ回路を持つセンサは、高電力密度システムを実現することができる。PCBセンサは,DCラインからの電流変化率を測定し,サンプルホールド(S/H)回路を備えたオペアンプ積分器が再生プロセスを完了させる。フルブリッジインバータに簡単な電流フィードバックコントローラを実装し検証を行った。

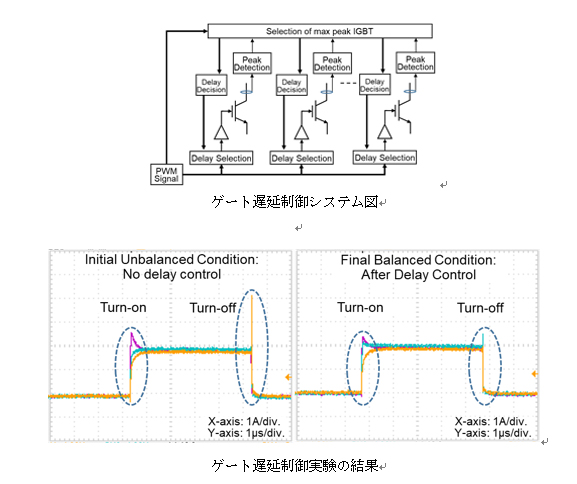

並列IGBTデバイスとミラーの電流均等化のためのゲート遅延制御プラトー効果

パワー半導体デバイスは大電流定格のために並列に動作させるが、並列動作に伴う電流アンバランスの問題がある。電流のアンバランスは、パワーデバイスのスイッチング時、すなわちダイナミックな電流共有時に深刻である。電流アンバランスを最小化するために、電流ピーク検出法に基づくゲート遅延制御技術を用いて、電流ピークに続いて、対応するゲート信号がナノ秒の分解能で遅延させる。独立したターンオンとターンオフの遅延制御により、並列接続されたパワーデバイス間の電流分担を最小化し、場合によっては均等化することができる。

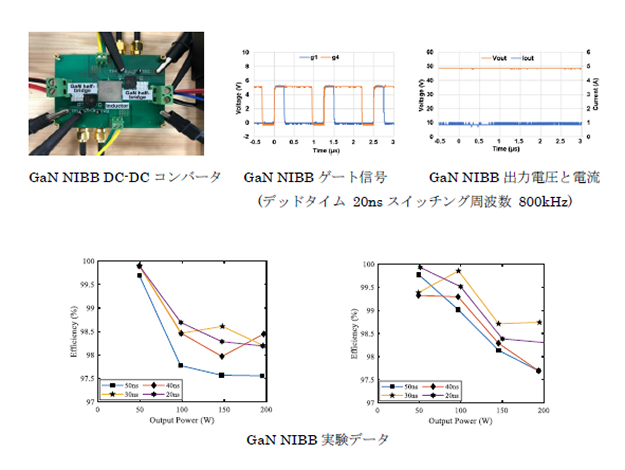

GaNベース非反転昇降圧DC-DCコンバータのスイッチング周波数によるデッドタイム評価

ワイドバンドギャップ・パワーデバイス GaN は高いスイッチング周波数で動作でき、ダイオードのような動作で第 3 象限で動作する利点がある。しかし、デッドタイム、すなわちゲートがオフの間の逆導通損失が大きくなる。また、この効果はスイッチング周波数や負荷条件に依存するため、電力変換器の動作にはこの現象を理解することが重要である。2つのGaNハーフブリッジを用いて非反転降圧(NIBB)DC-DCコンバータを構成した。NIBBコンバータは異なるスイッチング周波数条件とデッドタイム条件下で動作させ、デッドタイムは負荷条件とスイッチング周波数に対応して効率に大きな影響を与える。

特許公開リスト

| 公開番号 | 登録日・公開日 | 発明の名称 | 発明者 |

|---|---|---|---|

| 特許第7185879号 | 令和4年11月30日 | 半導体資料の評価方法 | 佐々木駿 大村一郎 |

| 特許第7156675号 | 令和4年10月11日 | 電力変換器、可変信号遅延回路及び電力変換方法 | 大村一郎 トリパシ ラビ ナス |

| 特許第7104917 | 令和4年7月13日 | 絶縁ゲートバイポーラトランジスタ装置、半導体装置の生産方法、及び、絶縁ゲートバイポーラトランジスタ装置の生産方法 | 大村一郎 佐藤克己 末代知子 |

| 特許第7043071号 | 令和4年3月18日 | 電流測定装置およびインバータ | 大村一郎 高原 賢 田畑勝次 長谷川一徳 附田正則 |

| 特許第6709918 | 令和4年3月9日 | ロゴスキ型電流センサ | 大村一郎 附田正則 |

| 特許第7019864号 | 令和4年2月4日 | 電力変換用半導体装置の状態推定システム及び状態推定方法 | 山口治之 椋木 誠 塚越昌彦 大村一郎 附田正則 管 理 渡辺和葉 |

| 特許第6718626号 | 令和2年6月17日 | "半導体検査装置" | 大村一郎 渡邉晃彦 附田正則 |

| 特許第6709425号 | 令和2年5月27日 | "半導体装置" | 附田正則 大村一郎 馬場昭好 |

| US 10,411,111,B2 | 2019年9月10日 | "METHOD FOR FABRICATIONG HIGH-VOLTAGE INSULATED GATE TYPE BIPOLAR SEMICONDUCTOR DEVICE" | Ichiro Omura Masahiro Tanaka Masanori Tsukurda Tamato Miki |

| 特許第6465348号 | 平成31年1月18日 | "電力用半導体デバイスのボンディングワイヤ電流磁界分布検出方法 及び装置" |

大村一郎 附田正則 田代勝治 篠原長勇喜 中野繁太 大胡田清一 長友一則 |

| 特許第6465349号 | 平成31年1月18日 | "電力用半導体デバイスのボンディングワイヤ電流磁界分布検査診断方法 及び装置" |

大村一郎 附田正則 田代勝治 松尾和顕 |

| 特許第6440175号 | 平成30年11月30日 | "高電圧絶縁ゲート型電力用 半導体装置 およびその製造方法" |

大村一郎 田中雅浩 附田正則 三木大和 |

| 特許第6288678号 | 平成30年2月16日 | "高電圧絶縁ゲート型電力用半導体装置 およびその製造方法" |

大村一郎 田中雅浩 附田正則 三木大和 |

| 特許第6153151号 | 平成29年6月9日 | 高電圧電力用半導体装置 | 大村一郎 瀬戸康太 附田正則 |

| 特許第6004988号 | 平成28年9月16日 | 電力用半導体素子のゲート制御装置 | 大村一郎 附田正則 三木大和 椋木誠 高尾健志 吉沢大輔 |

| 特許第5846421号 | 平成27年12月4日 | 半導体回路の電流測定装置 | 大村一郎 加生裕也 平井秀敏 附田正則 |

| 特許第5804494号 | 平成27年9月11日 | 半導体装置及びその駆動方法 | 大村一郎 松本泰明 津田基裕 附田正則 |

| 特許第5721137号 | 平成27年4月3日 | 半導体装置の短絡保護装置 | 大村一郎 湯淺一史 谷村拓哉 附田正則 |